Additionneur / Soustracteur 8 bits sur FPGA

Projet de première année de BUT GEII – Logique numérique et systèmes programmables

Présentation du projet

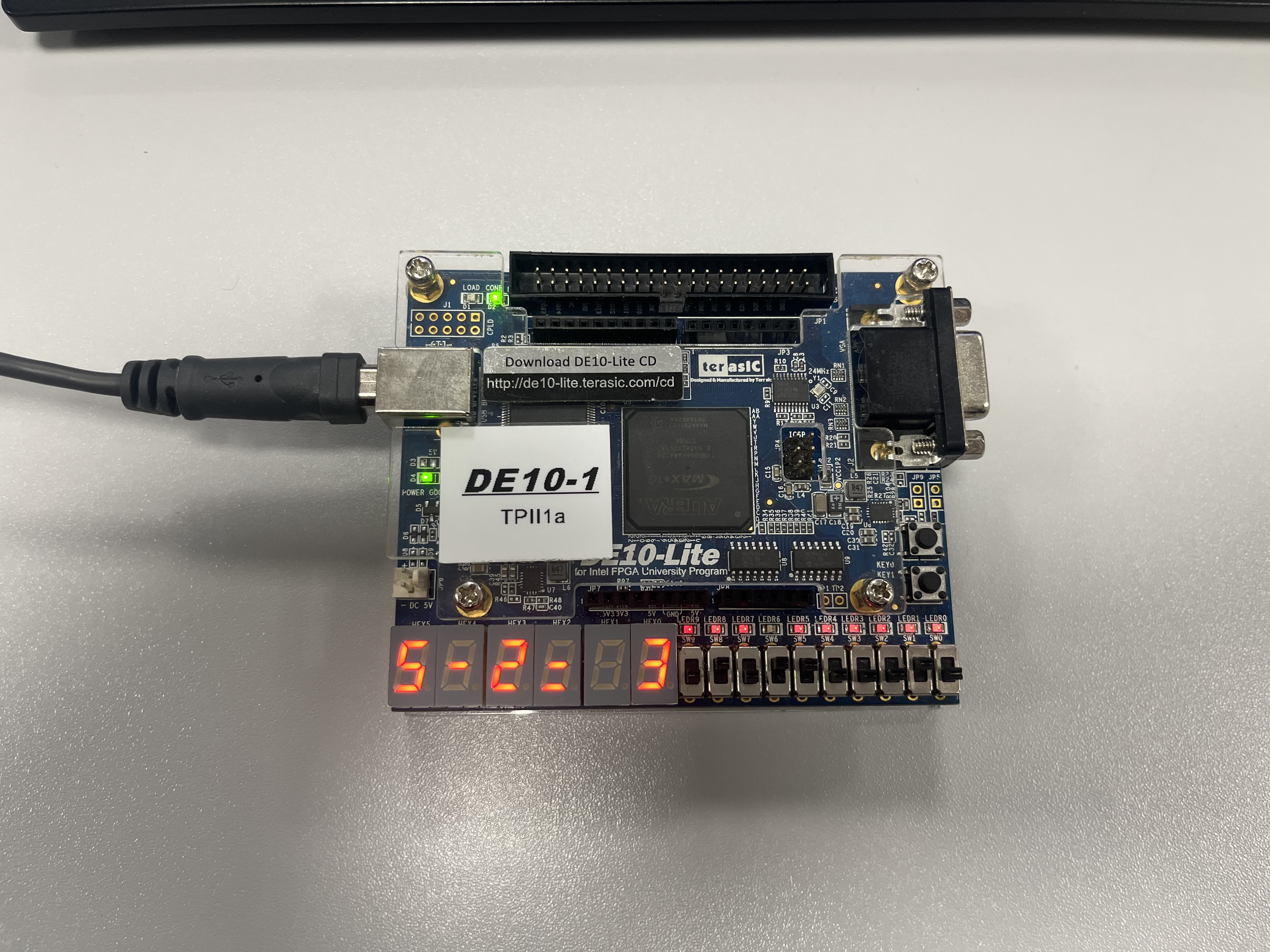

Dans le cadre des projets tutorés de première année, nous avons réalisé un additionneur / soustracteur sur 8 bits signés en utilisant une carte FPGA Intel DE10. Le système permet d’additionner ou de soustraire deux nombres sélectionnés à l’aide d’interrupteurs présents sur la carte.

L’objectif principal était de mettre en œuvre les principes de la logique combinatoire en concevant entièrement le circuit à l’aide de portes logiques dans le logiciel Quartus Prime, sans utiliser de blocs arithmétiques préconçus. Ce projet nous a permis de comprendre concrètement le fonctionnement interne des circuits de calcul numérique.

Fonctionnalités

- Sélection de deux nombres sur 8 bits signés via interrupteurs

- Choix du mode addition ou soustraction

- Calcul en logique combinatoire pure

- Affichage du résultat sur les afficheurs 7segments de la carte FPGA

- Gestion du signe et des dépassements

Technologies utilisées

Le projet a été développé sur une carte Intel DE10 équipée d’un FPGA, en utilisant le logiciel Quartus Prime pour la conception et la simulation des circuits numériques.

L’additionneur/soustracteur a été réalisé à partir de portes logiques fondamentales (ET, OU, NON, XOR...) ainsi que des multiplexeurs. Après avoir établi les tables de vérité nous avons réussi à permettre le calcul sur 8 bits. La soustraction a été implémentée par complément à deux.

Difficultés rencontrées

L’une des principales difficultés a été la gestion correcte des nombres signés et de la soustraction par complément à deux. Il a fallu bien comprendre la représentation binaire des nombres négatifs et adapter la logique du circuit pour obtenir des résultats cohérents dans tous les cas.

De plus, la conception entièrement en logique combinatoire a rapidement rendu le schéma complexe, avec un grand nombre de portes logiques. L’organisation du projet dans Quartus Prime et la vérification des signaux étaient nécessaires.

Galerie